# Impact of Bottom Electrode Integration on OxRAM Arrays Variability

N.-P. Tran, J. Sandrini, A. Persico, J.-F. Nodin, T. Magis, R. Crochemore, N. Castellani, M.-C. Cyrille, G. Molas, E. Nowak

#### ▶ To cite this version:

N.-P. Tran, J. Sandrini, A. Persico, J.-F. Nodin, T. Magis, et al.. Impact of Bottom Electrode Integration on OxRAM Arrays Variability. VLSI-TSA - 2020 International Symposium on VLSI Technology, Systems and Applications, Aug 2020, Hsinchu, Taiwan. pp.33-34, 10.1109/VLSI-TSA48913.2020.9203694. cea-03027403

## HAL Id: cea-03027403 https://cea.hal.science/cea-03027403

Submitted on 27 Nov 2020

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### Impact of Bottom Electrode Integration on OxRAM Arrays Variability

N.-P. Tran, J. Sandrini, A. Persico, J.-F. Nodin, T. Magis, R. Crochemore, N. Castellani, M.-C. Cyrille, G. Molas, E. Nowak

CEA-LETI, Minatec Campus, 17 rue des Martyrs, 38054 Grenoble Cedex 9, France, Nguyet-phuong.TRAN@cea.fr

#### ABSTRACT

HfO<sub>2</sub>-based OxRAMs with various metal stacks in the inferior VIA of bottom electrode were fabricated. We demonstrated for the first time that the metal stack of TiN PVD (physical vapour deposition), followed by an annealing step decreases the standard error of the forming voltage by 10% compared to the other variants. The related die-to-die and cell-to-cell variability is greatly reduced along the wafer diameter and the LRS shows better control of the tail bits at  $3\sigma$  of the distribution. The number of failed operations over 1e4 cycles for 1k cells is reduced by a factor 3, reaching a BER of 8e-5. Finally, correlation of the cell reliability with the bottom via roughness is discussed.

#### INTRODUCTION

Resistive Random-Access Memories (RRAMs) are extensively studied as a competitive candidate for future nonvolatile memory application due to their simple structure, fast switching speed and compatibility with silicon Complementary Metal-Oxide-Semiconductor CMOS technology [1-2]. However, the key obstacle for the use of metal oxide RRAM (OxRAM) is the relatively poor uniformity of the switching voltages and resistance states. Some studies investigate RRAM variability on single cell structures for a large number of cycles [3], thus considering the cycling variability but not the device-to-device one. Others works in literature dealt with array structures, although lacking information on the fundamental variability limits [4-6]. Moreover no correlation with process parameters was addressed. In this work, we focus on the impact of various metal stacks as inferior VIA of the bottom electrode (BE). The process-induced variability is studied as well as impact of die location on cycling variability. The results allowed us to benchmark the various bottom electrode integration processes and to relate the process variations to the electrical performances.

#### OxRAM TECHNOLOGY AND STRUCTURE

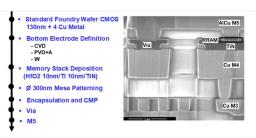

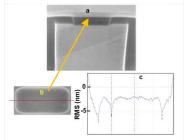

OxRAM technology was integrated on 130 nm CMOS logic. On top of Cu Metal 4, a BE is defined by three various metal stacks (Tab. 1) as inferior VIA and completed with the deposition of a 150nm TiN layer, acting as the bottom electrode of the memory. The remainders of the fabrication steps are exactly the same for the three investigated BE integrations. They consist in BE CMP, deposition of the HfO<sub>2</sub> 10nm/Ti 10nm/TiN memory stack and the completion of the back end of the device. A summary of the process steps, together with a cross section of a fully integrated 400nm device, are reported in Fig. 1.

The tests presented in this work have been performed on 4kb 1T-1R arrays developed within this platform. The word line (WL) is connected to the NMOS gate, setting the current compliance Icc. Forming and Set operations are performed by applying a positive voltage pulse on the bit line (BL) that is also the OxRAM top electrode, whereas Reset is performed by applying a voltage pulse on the source line (SL), contacted to the NMOS source.

#### FORMING VOLTAGE VARIABILITY

The first indicator used to evaluate the various BE integration processes is the forming voltage distribution. This parameter has the advantage of being (a) very sensitive to physical characteristics such as the electrode surface roughness, the insulator thickness and eventual oxide interface

residues, and (b) one critical parameter for OxRAMs integrated in scaled technology nodes, as the maximum BL voltage is frequently limited by the gate oxide thickness.

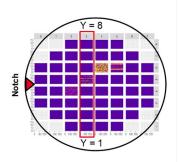

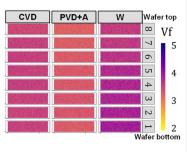

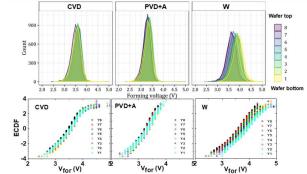

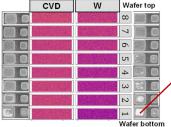

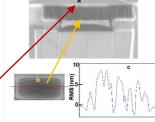

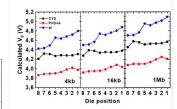

The forming voltage has been measured with a 1µs pulse sequence of increasing BL voltages from 2V to 5V, with a step of 0.1V. The 4kb arrays (8 matrices) along the wafer diameter chosen for this measurement are presented in Fig. 2. The heat maps reported in Fig. 3 and the forming voltage distributions in Fig. 4 show the differences between BE integrations and between matrices along the wafer diameter for each variant. The W variant is the least uniform: it has a larger process induced drift (top wafer = lower voltage). For W, which has a higher mechanical strength than TiN, a higher RMS roughness of its post CMP surface (Fig. 7b) is observed in comparison with the TiN one (Fig. 5b). Consequently, it can induce oxide residues on the BE surface (Fig. 6), corresponding to higher forming voltages. Both TiN splits have slight radial fluctuations, where annealed PVD TiN (PVD+A) has the tightest distribution. The anneal step improves the metal stack characteristics in terms of defectiveness and surface contact. Because the forming voltage is approximately normally distributed, we calculated the mean values and the standard deviation of the forming voltage to estimate the expected forming voltage needed to fully form 4kb, 16kb and 1Mb matrices (Fig. 8). The predicted values change considerably depending on the selected process, underlining the importance of reducing the forming voltages and the related variabilities, especially for large arrays.

#### ENDURANCE VARIABILITY

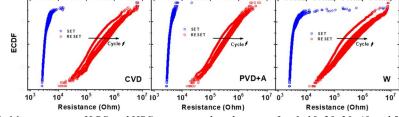

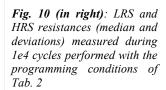

Cycle-to-cycle variability for the various BE integrations was addressed by cycling three 4kb matrices per wafer for 1e4 operations. The test protocol was the following: first, a forming operation with a write and verify algorithm (target R<1MOhm) is performed with 1µs pulses of increasing BL voltages from 2V to 5V and Icc of 25µA. Next, forming operation is followed by 1µs pulses ranging from 2.0 to 3.5V with a compliance of 260µA. Then, one matrix per variant (same position) was cycled 50 times with Vset 2.0, Icc 260µA, Vreset 1.8V. The results show that PVD+A has a better low resistance state distribution and less defectiveness with respect to the CVD and W variants (Fig. 9).

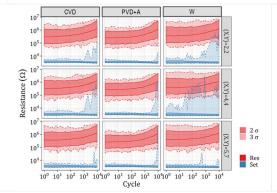

Finally, a 1e4 cycles test has been performed on three 4kb matrices with 3 conditions (Tab. 2). The results with the best condition are showed in Fig. 10, where a separation of high and low resistance states can be obtained at 3σ up to 1e4 cycles for PVD+A variant. We calculated the BER (Bit Error Ratio) for each matrix as the number of error bits over the total number of read operations. A summary of the mean BER differences for the various integration methods is reported in Fig. 11, where the PVD+A is significantly better than the other variants with a number of errors generally three times lower.

#### CONCLUSION

We fabricated OxRAM 1T1R arrays with various metal stack deposition as bottom electrode to improve memory reliability and reduce variability. A TiN PVD, followed by an anneal process, showed lower and more controlled forming voltages with lower dispersion, and a better BER over 1e4 cycles, attributed to a more uniform bottom electrode surface along the wafer and within the die.

This work is supported by the European WAKeMeUP Project, European commission, French government and Auvergne-Rhône Alpes Region.

#### REFERENCES

- [1] L. Perniola et al., IMW, 2016, pp. 1-3

- [2] Z. Chai et al., VLSI, 2016, pp. 122-123

- [3] D. Garbin, *IEDM*, 2014, p. 28.4.1-28.4.4

- [4] A. Grossi et al., IEDM Tech. Dig., 2016, pp.1-4

- [5] S.S. Sheu et al., ISSCC 2011, pp.200-202

- [6] G. Sassine et al., IRPS 20

| CVD                                         | PVD+A                                           | w                                         |

|---------------------------------------------|-------------------------------------------------|-------------------------------------------|

| TiN 350°C                                   | TIN 350°C                                       | TIN 350°C                                 |

| TIN 100°C                                   | TIN 100°C                                       | W 440°C<br>TiN 100°C                      |

| - CVD TiN at 200°C<br>- PVD Ti+TiN at 100°C | - PVD Ti+TiN at 100°C<br>- Anneal at 400°C (Ar) | - PVD Ti+TiN at 100°C<br>- CVD W at 440°C |

**Tab. 1**: Variants of metal stack in inferior VIA of OxRAM bottom electrode studied in this work

Fig. 1: Description of the process flow and SEM cross section of the integrated OxRAM

Fig. 2: Wafer map of 8 tested matrices along the wafer diameter

Fig. 3: Forming voltage heat-map per variant along wafer diameter

Fig. 4: Forming voltage distribution of 4kb arrays along wafer diameter for each variant. V<sub>BL</sub> from 2V to 5V with a 0.1V step

inferior VIA with TiN, (b) TiN surface post CMP, (c) TiN RMS surface scan

Fig. 5: (a) SEM cross-section of Fig. 6: SEM observation of bottom Fig. 7: (a) SEM cross-section electrode surface. For OxW, more of OxRAM BE with W in the oxide residues on the post oxide inferior VIA, (b) W surface post CMP surface along wafer diameter

CMP, (c) W RMS surface scan

Fig. 8: Predicted forming voltages to fully form 4kb, 16kb, 1Mb

| Conditions  |                  |                    |  |

|-------------|------------------|--------------------|--|

| Cdt number  | V <sub>set</sub> | V <sub>reset</sub> |  |

| 1           | 2.1              | 1.8                |  |

| 2           | 2                | 1.8                |  |

| 3           | 2                | 1.7                |  |

| Common: pul | se width 1       | ıs, Icc 260µA      |  |

Tab. 2: Summary of programming conditions applied on the tested arrays

Fig. 9: Measurement of LRS and HRS resistance distributions after 1, 10, 20, 30, 40 and 50 cycles on one matrix per wafer performed with the programming conditions of Tab. 2

Fig. 11: Mean BER differences between various integration methods