# Stacked-Wires FETs for advanced CMOS scaling

S. Barraud<sup>1</sup>, V. Lapras<sup>1</sup>, M.P. Samson<sup>2</sup>, B. Previtali<sup>1</sup>, J.M. Hartmann<sup>1</sup>, N. Rambal<sup>1</sup>, C. Vizioz<sup>1</sup>, V. Loup<sup>1</sup>, C. Comboroure<sup>2</sup>, F. Triozon<sup>1</sup>, N. Bernier<sup>1</sup>, D. Cooper<sup>1</sup>, M. Vinet<sup>1</sup>

<sup>1</sup> CEA, LETI, MINATEC Campus and Univ. Grenoble Alpes, 38054 Grenoble, France, email: <a href="mailto:sylvain.barraud@cea.fr">sylvain.barraud@cea.fr</a>

<sup>2</sup> STMicroelectronics, 850 rue J. Monnet, 38920 Crolles, France.

### **Abstract**

We present recent progress on vertically stacked-wires MOSFETs with a replacement metal gate process for CMOS scaling beyond FinFET technology. Key technological challenges (such as 3D integration process including inner spacer, mobility, and strain engineering) will be discussed in relation to recent research results.

#### 1. Introduction

Gate-All-Around (GAA) field-effect-transistors have long been recognized as offering the best solution to short-channel-effects (SCE) with a high current drivability per layout footprint due to 3D vertically stacked channels [1-4]. Moreover, horizontal GAA NanoWires (NWs) also have the advantage of being fabricated with minimal deviation from Fin-FET devices in contrast to vertical NWs which require more disruptive technological changes. For these reasons, the GAA stacked-wires MOSFET architecture is today regarded as an attractive option to push CMOS scaling beyond 7/5nm nodes. Although the first 3D GAA transistors were demonstrated ten years ago [1-4], significant progress have been reported last year [5-6] with aggressive 44/48 CPP (Contacted Poly Pitch) ground rules [7]. In this paper we will discuss recent progress and the major roadblocks remaining to reach higher performances in such devices, in particular stress boosters and parasitic capacitances.

## 2. Design options of GAA stacked-wires devices

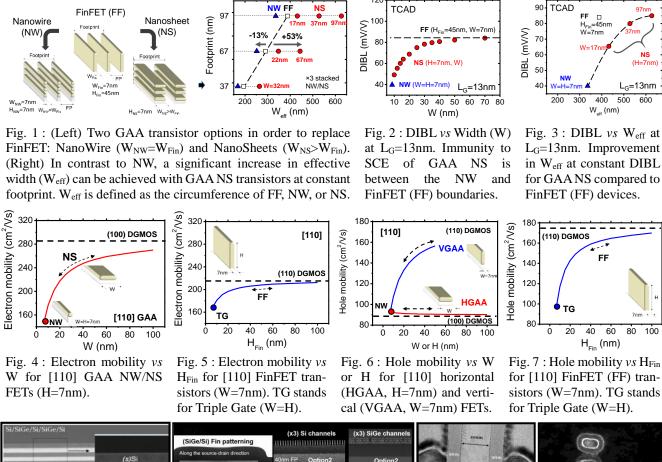

Two main options can be considered for GAA transistors (**Fig. 1**). As compared to FinFET, the conventional square (or round) NW has a lower effective width ( $W_{\rm eff}$ ) in a given layout footprint even if the Drain-Induced Barrier Lowering (DIBL) shown in **Fig. 2** is strongly reduced. However, wide and thin Nanosheets (NS) can significantly increase  $W_{\rm eff}$  compared to conventional FinFETs (or stacked-NW) and therefore offer better current drivability. As shown in **Fig. 3**, stacked nanosheets show the best compromise to maximize  $W_{\rm eff}$  while having similar and even lower DIBL. The capability to have a fine-tuning of the sheet width enables  $V_{\rm T}$  flavors relevant for power-performance optimization [7,8,9].

## 3. Carrier mobility

The computed carrier mobilities in [110]-oriented GAA NS, NW and FinFET devices are shown in **Figs. 4-7**. The size-dependent carrier mobility in 3D multi-gate devices is mainly due to facet-dominated transport with high (resp. low) electron mobility in the (100) (resp. (110)) plane and high (resp. low) hole mobility in the (110) (resp. (100)) plane. Meanwhile, mobility in conventional NWs is often the worse due to additional quantum confinement effects resulting in mobility reduction. Horizontal GAA NS for n-FET and vertical GAA NS for p-FET turn out to be the best possible configuration to promote electron and hole transport.

## 4. Device integration and performance

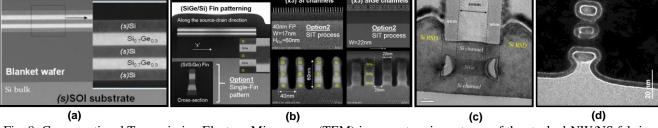

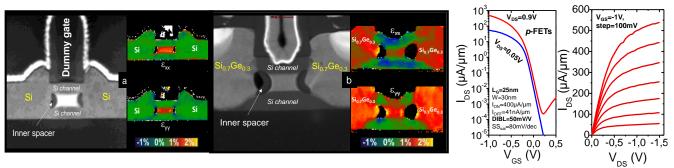

Over the last year, vertically stacked-NW/NS MOSFETs were fabricated using a replacement metal gate process with specific technical requirements compared to FinFET [5-7]. The fabrication started with the epitaxial growth of  $(Si_{0.7}Ge_{0.3}/Si)$  multilayers. **Fig. 8a** shows a TEM image of (SiGe/Si) multilayers with three Si channels and two sacrificial SiGe layers. Then, individual and dense arrays of fins were patterned to fabricate stacked-wires FETs. Multiple patterning techniques were used in order to meet the density targets of advanced nodes. Fig. 8b shows TEM images in the transverse and longitudinal directions after the etching of (SiGe/Si)-fins. Our SIT-based patterning technique yielded 40 nm-pitch fins which were 60 nm high and roughly 20 nm wide. After that, dummy gates and spacers were defined prior to the anisotropic etching of the (SiGe/Si) multilayers. Then, the SiGe layers were partially etched selectively to the Si ones to form inner spacers well-aligned and correctly dimensioned as shown in Fig. 8c. The Si wires were released during the Replacement Metal Gate (RMG) module prior to conformal HfO<sub>2</sub>/TiN/W gate deposition (**Fig. 8d**). If the fabrication of stacked-wires FETs including inner spacer is crucial to reduce parasitic capacitances, another major challenges is the strain engineering used to improve short-channel performances. Strain fields were imaged at different stages of our fabrication process. For example, SiGe(B) raised-Source/Drain were used to inject a significant amounts of compressive strain in Si channels (**Fig. 9b**). The level of in-plane deformation in Si p-channels became close to 1%. Meanwhile, no strain was generated with Si raised-S/Ds (Fig. 9a). A typical transfer and output characteristics of stacked-NWs p-FET with  $L_G=25$  nm and W~30 nm is shown in **Fig. 10**.

### 5. Conclusion

Recent results in stacked Nanosheet transistors demonstrate the high competitiveness of this technology for future technology nodes. Thanks to the benefits of large  $W_{\text{eff}}$ , the Nanosheet architecture is a versatile design option for performance and power management.

## Acknowledgements

This work was partly funded by the French Public Authorities through the NANO 2017 program. It is also partially funded by the SUPERAID7 (grant  $N^{\circ}$  688101) project.

### References

[1] T. Ernst *et al.*, IEDM, 10.1109/IEDM.2006.346955, 2006, [2] L.K. Bera *et al.*, IEDM, 10.1109/IEDM.2006.346841, 2006, [3] C. Dupré *et al.*, IEDM, 10.1109/IEDM.2008.4796805, 2008, [4] E. Bernard *et al.*, VLSI, pp. 16-17, 2008, [5] H. Mertens *et al.*, VLSI, 10.1109/VLSIT.2016.7573416, 2016, [6] S. Barraud *et al.*, IEDM, 10.1109/IEDM.2016.7838441, 2016, [7] N. Loubet *et al.*, VLSI, 10.1109/VLSIT.2017, 2017, [8] S.-D. Kim *et al.*, S3S conference, 10.1109/S3S.2015.73335212015, [9] L. Gaben *et al.*, SSDM conference, 2015.

Fig. 8: Cross-sectional Transmission Electron Microscopy (TEM) images at various stages of the stacked-NW/NS fabrication process. (a) Formation of (Si/SiGe) superlattices with 3 levels of Si layers stacked upon one another. (b) Etching of (Si/SiGe) fins shown in the longitudinal and transverse directions of future Si (or SiGe) wires. Two fins patterning were used: (*left*) single-fin process and (*right*) dense array of fins with a Sidewall Image Transfer (SIT) process. (c) Stacked-wires FET after the integration of inner spacer. (d) Stacked-wires FET with a HfO<sub>2</sub>/TiN/W gate stack.

Fig. 9: HAADF STEM images of stacked-NWs p-FETs and Precession Electron Diffraction deformation maps in the  $(\epsilon_{xx})$  and  $(\epsilon_{yy})$  directions. Strain is measured after Si (a) and Si<sub>0.7</sub>Ge<sub>0.3</sub>:B (b) S/D epitaxy. No strain into Si p-channels for Si S/Ds. However, recessed and epitaxially regrown Si<sub>0.7</sub>Ge<sub>0.3</sub>:B S/Ds inject a compressive strain close to 1% (in blue) in the top and bottom Si p-channels.

Fig. 10: (*Left*)  $I_{DS}$ - $V_{GS}$  and (*right*)  $I_{DS}$ - $V_{DS}$  characteristics of stacked-NS *p*-FETs with  $L_G$ =25nm. Here, the width W~30nm.